# INTRODUCTION TO IA-32

Jo, Heeseung

### IA-32 Processors

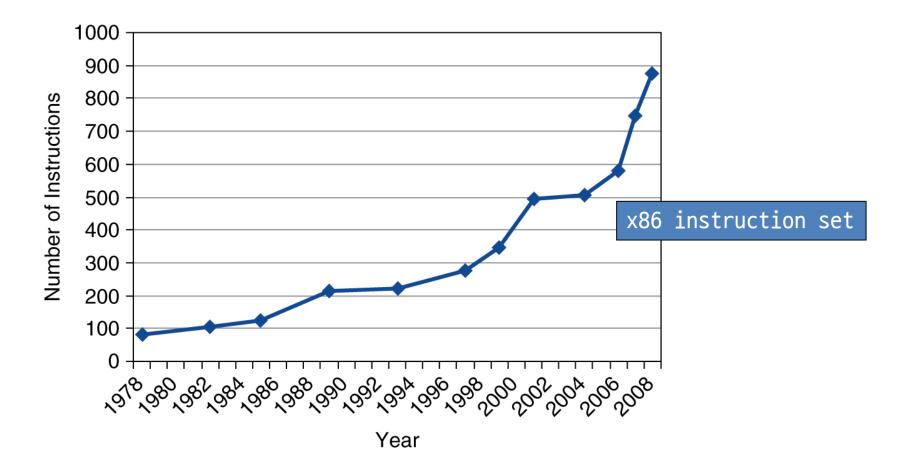

Evolutionary design

- Starting in 1978 with 8086

- Added more features as time goes on

- Still support old features, although obsolete

- Totally dominate computer market

Complex Instruction Set Computer (CISC)

- Many different instructions with many different formats

- Hard to match performance of Reduced Instruction Set Computers (RISC)

- But, Intel has done just that!

### Intel's Backward Compatibility

Instruction set doesn't change

But they do accrete more instructions

### IA-32 History

#### Evolution with backward compatibility

| 1978 | 8086               | x86 is born    |

|------|--------------------|----------------|

| 1980 | 8087               | x87 is born    |

| 1985 | 80386              | "IA-32"        |

| 1995 | Pentium Pro        | PAE            |

| 1997 | Pentium MMX        | MMX            |

| 1999 | Pentium III        | SSE            |

| 2000 | Pentium 4          | SSE2           |

| 2004 | Pentium 4 Prescott | SSE3, Intel 64 |

| 2005 | Pentium 4 662      | Intel VT       |

| 2006 | Core 2             | SSSE3          |

| 2008 | Core 2 Penryn      | SSE4.1         |

| 2008 | Core i7            | SSE4.2         |

### Intel x86 Processors: Overview

| Architectures |       | ectures  | Processors            |      |

|---------------|-------|----------|-----------------------|------|

|               |       | X86-16   | 8086                  |      |

|               |       |          | 286                   | _    |

|               | X86   | -32/IA32 | 386<br>486<br>Pentium |      |

|               |       | MMX      | Pentium MMX           | _    |

|               |       | SSE      | Pentium III           | _    |

|               |       | SSE2     | Pentium 4             | _    |

|               |       | SSE3     | Pentium 4E            |      |

| X             | 86-64 | / EM64t  | Pentium 4F            | time |

|               |       | SSE4     | Core 2 Duo<br>Core i7 |      |

IA: often redefined as latest Intel architecture

# Intel x86 Evolution: Milestones

| Name  | Date                                                                       | Transistors         | MHz                     |

|-------|----------------------------------------------------------------------------|---------------------|-------------------------|

| 8086  | 1978                                                                       | 29K                 | 5-10                    |

| •     | First 16-bit processor<br>1MB address space                                | (Basis for IBM PC a | & DOS)                  |

| 386   | 1985                                                                       | 275K                | 16-33                   |

| •     | First 32-bit processor<br>Added "flat addressing<br>Capable of running Uni | J''                 | 32                      |

| •     | 32-bit Linux/gcc uses                                                      | no instructions int | roduced in later models |

| Penti | um 4F 2004                                                                 | 125M                | 2800-3800               |

| •     | First 64-bit processor                                                     | , referred to as x8 | 6-64                    |

| Core  | i7 2008                                                                    | 731M                | 2667-3333               |

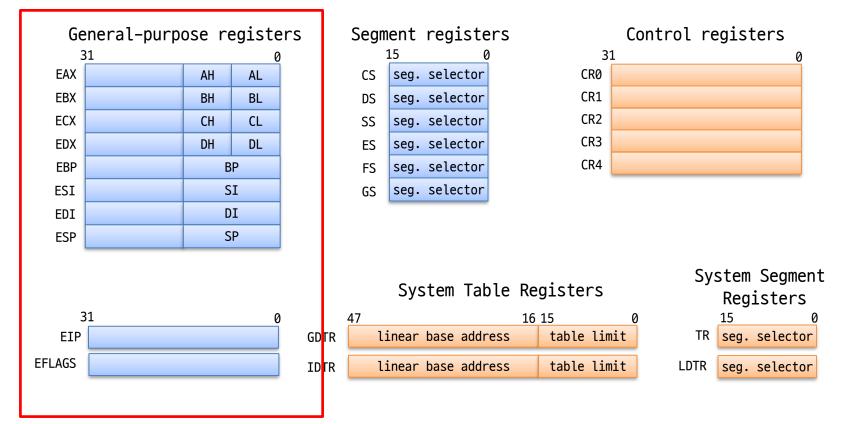

# Basic Execution Environment

#### Application Programming Registers

### Integer Registers (IA32)

#### Origin (mostly obsolete)

general purpose

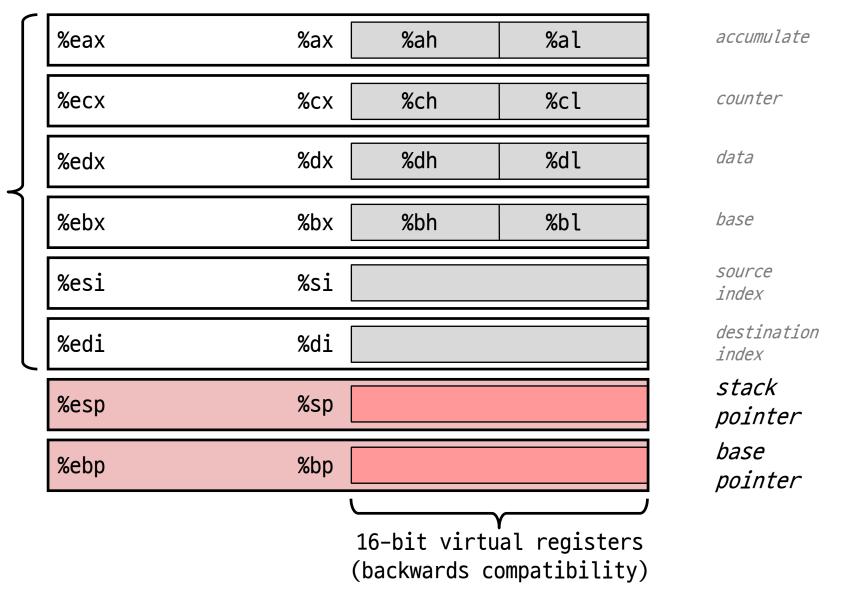

### General-Purpose Registers

#### EAX, EBX, ECX, EDX, ESI, EDI, ESP, EBP

- EAX: Accumulator for operands and results data

- **EBX:** Pointer to data in the DS segment

- **ECX:** Counter for string and loop operations

- EDX: I/O pointer

- ESI: Pointer to data in the segment pointed to by the DS register; Source pointer for string operations

- EDI: Pointer to data in the segment pointed to by the ES register; Destination pointer for string operations

- **ESP:** Stack pointer (in the SS segment)

- **EBP:** Pointer to data on the stack (in the SS segment)

# EFLAGS Register (1)

|                                                                                                                                                                                                                                                                                                                                                                                    | 31                                                                                    | 30                                             | 29                                     | 28                                 | 27  | 26  | 25 | 24 | 23 2 | 2 2 | 21.2 | 20          | 19          | 18     | 17     | 16     | 15 | 14     | 13 12   | 11     | 10     | 9     | 8      | 7      | 6      | 5 | 4      | 3 | 2      | 1 | 0      |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------|------------------------------------------------|----------------------------------------|------------------------------------|-----|-----|----|----|------|-----|------|-------------|-------------|--------|--------|--------|----|--------|---------|--------|--------|-------|--------|--------|--------|---|--------|---|--------|---|--------|

|                                                                                                                                                                                                                                                                                                                                                                                    | 0                                                                                     | 0                                              | 0                                      | 0                                  | 0   | 0   | 0  | 0  | 0    |     | D    | V<br>I<br>P | V<br>I<br>F | A<br>C | ∨<br>M | R<br>F | 0  | N<br>T | I O P L | O<br>F | D<br>F | <br>F | T<br>F | S<br>F | Z<br>F | 0 | A<br>F | 0 | P<br>F | 1 | C<br>F |

| <ul> <li>X ID Flag (ID</li> <li>X Virtual Inter</li> <li>X Virtual Inter</li> <li>X Alignment C</li> <li>X Virtual-8086</li> <li>X Resume Fla</li> <li>X Nested Task</li> <li>X I/O Privilege</li> <li>S Overflow Fla</li> <li>X Interrupt Ena</li> <li>X Trap Flag (T</li> <li>S Sign Flag (S</li> <li>S Zero Flag (Z</li> <li>S Auxiliary Ca</li> <li>S Parity Flag (</li> </ul> | rru<br>rup<br>he<br>Mag<br>k (l<br>ag<br>abl<br>E)<br>SF)<br>SF)<br>2F)<br>rry<br>(PF | it F<br>ck<br>od<br>(R<br>NT<br>(C<br>(C<br>le | Fla<br>(A<br>F)-<br>el (<br>DF)<br>Fla | g (<br>\\C<br>(\VI<br>)<br>]<br>ag | (IF | -)- |    |    |      |     |      |             |             |        |        |        |    |        |         |        |        |       |        |        |        |   |        |   |        |   |        |

- S Indicates a Status Flag

- C Indicates a Control Flag

- X Indicates a System Flag

Reserved bit positions. DO NOT USE. Always set to values previously read.

# EFLAGS Register (2)

Status flags

- CF (Carry): set if an arithmetic operation generates a carry or a borrow; indicates an overflow condition for unsigned-integer arithmetic

- PF (Parity): set if the least-significant byte of the result

contains an even number of 1 bits

- AF (Adjust): set if an arithmetic operation generates a carry or a borrow out of bit 3 of the result; used in binary-coded decimal (BCD) arithmetic

- ZF (Zero): set if the result is zero

- SF (Sign): set equal to the most-significant bit of the result

- OF (Overflow): set if the integer result is too large a positive number or too small a negative number to fit in the destination operand; indicates an overflow condition for signed-integer arithmetic

- DF (Direction): setting the DF causes the string instructions to auto-decrement; set and cleared by STD/CLD instructions

## Instruction Pointer

#### EIP Register (Program Counter, PC)

- Contains the offset in the current code segment for the next instruction to be executed

- Advanced from one instruction boundary to the next in straightline code, or

- Moved ahead or backwards by instructions such as JMP, Jcc, CALL, RET, and IRET

- Cannot be accessed directly by software

- EIP is controlled implicitly by control transfer instructions, interrupts, and exceptions

- Because of instruction prefetching, an instruction address read from the bus does not match the value in the EIP register

# Assembly Characteristics (1)

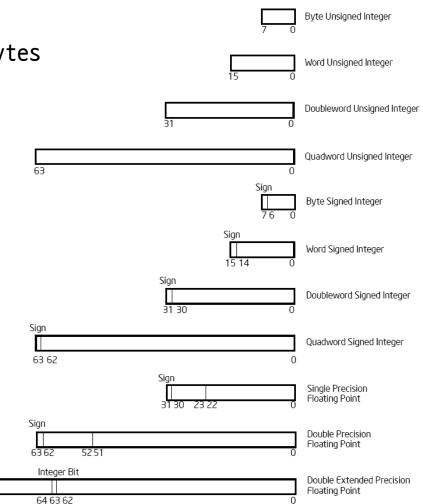

#### Minimal data types

- "Integer" data of 1, 2, 4, or 8 bytes

- Data values

- Addresses (untyped pointers)

- "Floating point" data of 4, 8, or 10 bytes

- No aggregate types such as arrays or structures

- Just contiguously allocated bytes in memory

Sign

7978

• (cf.) In IA-32, a "word" means 16-bit data

# Assembly Characteristics (2)

Three primitive operations

- Perform an arithmetic/logical function on register or memory data

- Transfer data between memory and register

- Load data from memory into register

- Store register data into memory

- Transfer control

- Unconditional jumps

- Conditional branches

- Procedure calls and returns

### IA-32 Reference

Intel 64 and IA-32 Architectures Software Developer's Manual

- Volume 1: Basic Architecture

- Volume 2A, 2B: Instruction Set Reference

- Volume 3A, 3B: System Programming Guide